出版社: 清华大学

原售价: 139.00

折扣价: 98.80

折扣购买: 抗辐射集成电路设计理论与方法(精)

ISBN: 9787302505297

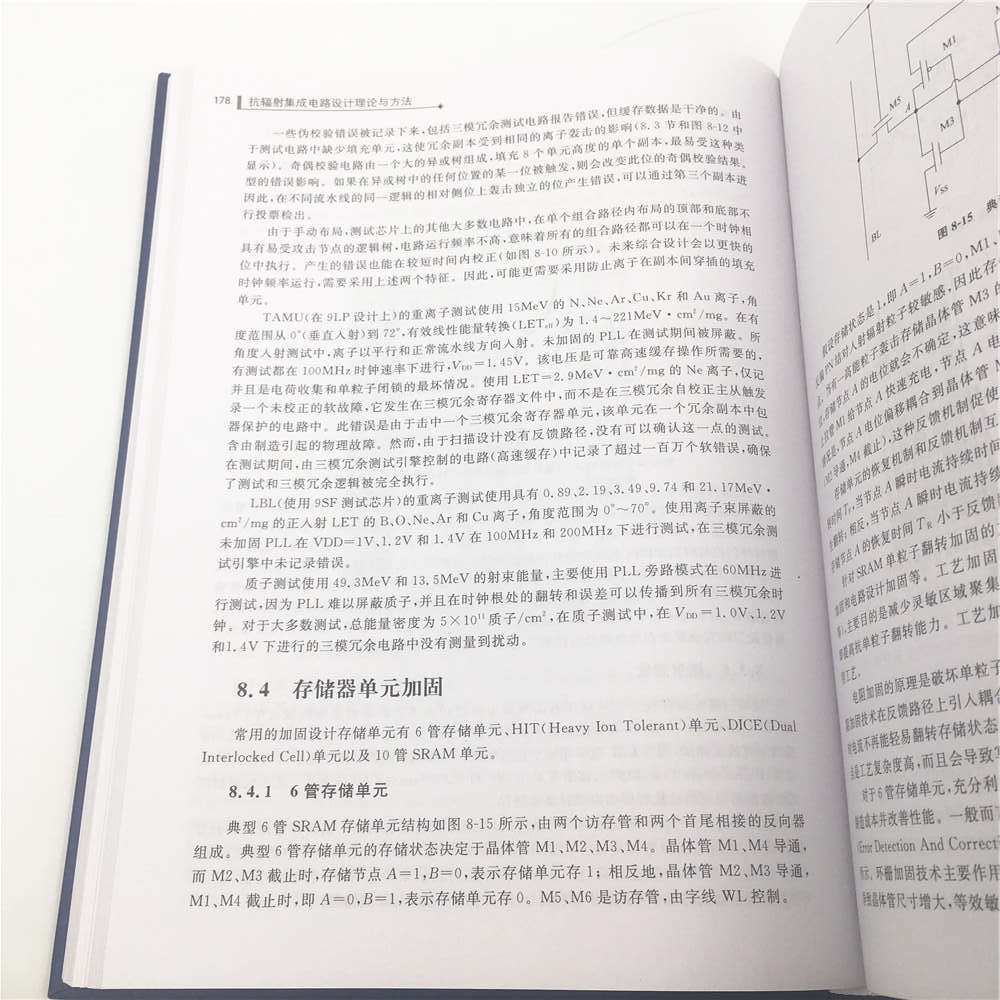

第3章电离总剂量效应 3.1概述 随着CMOS工艺尺寸的缩小,器件的总剂量效应也随之发生改变。硅局部氧化隔离(Local Oxidation of Silicon,LOCOS)技术使用了很多年,但是到了深亚微米工艺节点,由于鸟嘴区域的**缩小和静电效应,普遍采用浅沟*缘体(ShallowTrench Isolation,STI)代替LOCOS*缘体。LOCOS和STI两种晶体管的透射电子显微照片如图31所示[1,2]。 图31透射电子显微照片 在亚100nm节点情况下,体硅CMOS器件的SiO2栅氧缩小为*小的尺寸,几乎消除了由于电离总剂量辐射诱发在超薄栅氧中的电荷积累产生的阈值电压漂移[3]。因此,在大多数体硅CMOS工艺中主要的电离总剂量效应主要表现为浅沟*缘体中的电荷积累[4]。*缘体中的电荷诱捕,特别是沿着沟道氧化物侧墙的Si/SiO2界面,产生泄漏电流通路,形成NMOS晶体管关断状态漏源泄漏电流[6]。这个效应可以由图32来解释。其中,图32(a)为NMOS晶体管边沿漏电通路的正视图,图32(b)为器件的横截面图,在STI中产生氧化物俘获正电荷积累,从而诱发泄漏电流[4]。 图32电流总剂量诱发泄漏电流 同时,工艺尺寸缩小使得一些抗辐射加固设计结构如环栅器件无法使用,由于制造和光照设计规则的限制。W尺寸较大的器件往往采用叉指版图,产生多个有源区/STI边沿。理解决定边沿相关的泄漏电流及其变化规律的各种因素是**重要的。 在MOS集成电路开发之初,硅氧化物曾是主要的栅*缘体。**集成电路工艺需要获得驱动电流,栅*缘体变得越来越薄,已经到了电子遂穿的临界点,极大地增加了功耗。为了克服这个问题,使用高介电常数的栅*缘体是另外一种办法。通过使用高介电常数的栅材料,使用*厚*缘体可以获得与薄栅相同的等效电容,减小电子遂穿效应。但是,采用高介电常数材料代替SiO2会导致两个问题: 阈值电压钉扎(threshold voltage pinning)和声子散射(phonon scattering)都限制晶体管开关态速度。解决方案就是使用金属栅,对于NMOS和PMOS使用不同类型的金属。在选择栅金属材料中,金属栅的工作机理需要较多考虑,因为它决定了MOS管的阈值电压。 对于硅工艺的限制,*缘体上硅(SiliconOnInsulator,SOI)工艺是一个可以预见的替代方案。同体硅工艺相比,显著的优势是短沟道效应免疫、寄生的结电容减小及*小的工艺变化敏感性。但是,除了STI积累正电荷外,SOI埋层的电荷诱捕也影响TID灵敏性。因此,对于理解SOI器件在STI和SOI埋层中的电荷诱捕也一样重要。 研究CMOS器件的电离总剂量需要采用实验(X射线器件或钴源)和TCAD仿真,以此研究CMOS工艺缩小带来的总剂量效应的变化。在**的CMOS工艺和SOI工艺中,边沿相关的泄漏电流的总剂量敏感性参数主要包括STI工艺变化、侧墙掺杂变化及版图相关应力效应。 3.2电离总剂量 3.2.1电离损伤概述 靶材的电离是由高能光子或带电粒子(如质子、电子或高能重粒子等)与该材料原子发生反应造成的[10]。当光子材料相互作用发射次级电子,沿着这些次级电子发射轨迹生成电子空穴对,这时,光子诱发的电离损伤就开始了。光子和其他带电粒子也产生电子空穴对,从而导致电离损伤。 沿着带电粒子轨迹生成的电子空穴对的密度正比于靶材的沉积能量[11]。阻止本领或线性能量转换(Linear Energy Transfer,LET),代表了粒子的单位长度的能量损失(dE/dx),也是粒子质量、能量和靶材密度的函数[12]。LET的单位为MeV·cm2/mg。如图33所示,描述了电子和质子的能量与LET的关系。在低能区,质子的LET相对高于电子。但是,随着能量的增大,质子的LET迅速减小。电子的LET是非单调变化的,当能量小于约1MeV时,电子的LET减小,当能量高于约1MeV时,电子的LET增加。导致电子空穴对产生的由一个粒子沉积的总能量称作电离总剂量(Total Ionizing Dose,TID)。TID的典型单位为拉德(rad),代表一种材料单位质量吸收的能量。1rad(material)等效于100ergs/g。即1rad(material) =100ergs/g=6.24×1013eV/g。TID的另一个单位是格瑞(Gary,Gy),1Gy=100rad。由定义可知,能量损失与靶材的密度有关,因此,一般对硅及其氧化物分别称为rad(Si)及rad(SiO2)。利用转换因子可以得到1rad(Si)=0.58rad(SiO2)=0.94rad(GaAs)。 图33电子和质子阻止本领随粒子能量变化的示意图[12] 从由电离辐射导致的能量初始沉积到电离缺陷产生的物理过程如下: (1) 电子空穴对的生成。 (2) 小部分生成电子空穴对的快速复合。 (3) 残留在氧化物中的自由载流子的输运。 (4) 在缺陷前兆区域(defect precursor sites)经过空穴俘获的俘获电荷的形成,或经过与氢相关的反应界面态俘获的形成。 这些过程可以用图34来描述[14]。 图34电离总剂量损伤的主要过程[14] 在电子空穴对产生(过程1)中,入射粒子的动能的一部分损失以产生电子空穴对。使材料电离所需的平均能量Ep取决于靶材料的带隙能。因此,对于给定剂量产生的电子空穴对的数量强烈依赖于Ep以及材料密度。对于三种材料GaAs、Si和SiO2的电离能、材料密度和产生的载流子之间的关系列于表31中。 表31电离能、物质密度和生成的载流子之间的关系 材料平均电离能Ep/eV材料密度/g·cm-3每rad产生的电子空穴对密度 κg/pairs·cm-3 GaAs约4.85.32约7×1013 Si3.62.3284×1013 SiO2172.28.1×1012 使用式(31)可获得每rad的电子空穴对密度κg(表31第4列): κg#ehpcm3rad=100ergg1rad·11.6×10-12eVerg·1Ep#ehpeV·ρgcm3(31) 一旦产生,一部分电子空穴对通过柱状或成对复合湮灭(过程2)[11]。逃逸这个初始复合过程的电子空穴对数量除以产生的电子空穴对的总数即电子空穴对产生率,由fy表示。图35绘制了不同辐射类型的函数fy [14,15]。该图还描绘了电子空穴对复合是材料内电场的函数[16]。电子空穴对的产生率随着局部电场增加而单调增加。通常认为,具有比氧化物中的空穴高得多的迁移率的电子被快速地从电介质中扫除[17]。剩余的孔将通过SiO2中的浅陷阱进行极化子跳跃输运(过程3)[17]。这些输运空穴的一部分可以落入氧化物本体中或Si/SiO2界面附近的深陷阱中,从而形成俘获的正电荷(过程4前一步)[17]。空穴俘获效率也是氧化物中电场的函数[10]。陷阱空穴缺陷可能取决于其接近界面,通过电子隧道与下面的硅衬底交换电荷[18,19]。空穴和含氢缺陷或掺杂络合物之间的反应还可导致形成第二类型的电离缺陷: 界面态陷阱(过程4后一步)[20,21]。3.2.2节和3.2.3节提供了氧化物俘获电荷和界面态陷阱的性质的*详细的讨论。 图35在SiO2中未复合空穴的产生率为材料中的电场的函数[14,15] 3.2.2氧化物俘获电荷 1. 缺陷的性质 由于在中性氧空位中俘获空穴以及随后形成氧空位缺陷或陷阱缺陷中心E′[2227],氧化物俘获的电荷通常是净正的。E′主要有两种类型: E′δ和E′γ。E′δ是“二聚体”空位,其对氧化物中的空穴形成相对浅的陷阱,主要分布于整个SiO2体中,能级位于SiO2中间能隙带中大约1eV范围内的位置 [25],E′δ的浅陷阱能级能够让氧化层中的空穴通过或进行步进式跳跃输运过程了[25]。E′γ是一个相对*深的陷阱,其SiO2中间能隙带中的能级位置都大于3eV [23,25]。虽然E′γ可以位于整个氧化物中,但其中的大多数位于Si/SiO2界面附近[1719]。 两种类型的E′都可以与相邻的硅层交换电荷[23]。E′与硅“相通”的能力是其与界面距离的强函数[18]。易于从相邻硅俘获载流子或将载流子发射到相邻硅的E′通常称为边界陷阱或开关态。它们通常位于Si/SiO2界面3nm以内,并且可以通过电子隧道在微秒到秒的时间尺度上交换电荷[18,19]。位于距界面距离大于3nm的(即在氧化物本体中)的E′γ也可以俘获和发射载流子,但是该过程发生的可能性较低。因此,氧化物本体中的E′γ通常被视为固定(即与偏置无关)的正氧化物电荷(Not)。Not的移除或补偿需要在相对长的时间段内升高温度进行退火。图36中描绘了MOS器件中的边界陷阱(开关态状态)和氧化物俘获电荷(固定状态)的位置。氧化物中的电荷累积可以表示为[28,29] ΔNot=Dκgfyfottox(32) 式中: D为沉积的总电离剂量。 图36SiO2中俘获电荷的位置和稳定性[19] 从式(32)中可以看出,ΔNot与氧化物的厚度成比例。 2. 对CMOS直流响应的影响 固定氧化物俘获电荷可能对CMOS器件和集成电路的直流参数有重大影响。其中,一个*重要的影响是n沟道MOSFET和p沟道MOSFET的直流漏极电流对栅源电压Vgs的负偏移。这种效果如图37所示。图37描绘了对于固定的Id和辐射引起的Not累积使Vgs偏置点*趋向于负(通过ΔVot)偏移。在n沟道MOSFET中,这种偏移导致阈值电压的降低以及截止态电流和驱动电流的增加。在p沟道MOSFET中,Vt负向增加,驱动电流减小。 图37固定氧化物俘获电荷对NMOS和PMOS器件的影响 辐射诱发的直流电压漂移可以使用以下公式计算: "1. ****从微电子系统角度总结了**外辐射环境和辐射效应等方面的知识和技术。 2. ****披露辐射环境模拟和结合集成电路仿真的多层次辐射效应数值仿真技术。 3. ****介绍基于商用CMOS集成电路工艺的集成电路的抗辐射加固设计方法学。 4. 理论和实际相结合,系统总结了经典CMOS集成电路的抗辐射加固设计策略和电路。"